Why Your C Code Crashes on ARM Microcontrollers

17 min read Discover common reasons C code crashes on ARM microcontrollers and learn practical solutions for robust embedded development. (0 Reviews)

Why Your C Code Crashes on ARM Microcontrollers

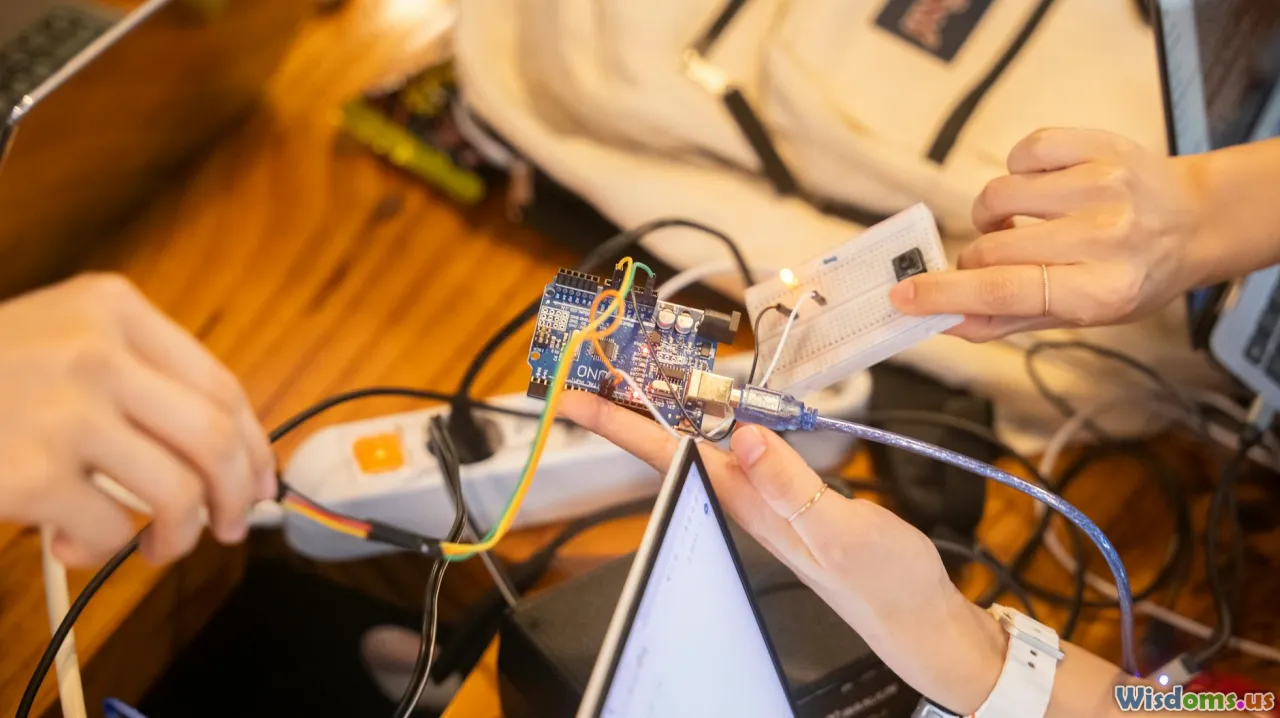

From developing IoT sensors to building high-speed embedded applications, ARM-based microcontrollers power countless modern devices. Yet, many C developers transitioning to ARM encounter baffling crashes and instability, even with code that ran smoothly on other platforms like x86. Faulty programs on microcontrollers not only hamper development but can also endanger hardware and mission-critical operations.

What causes these hard-to-debug failures? Let’s dive deep into the underlying reasons C code running on ARM MCUs is prone to crashing—and reveal how to prevent such setbacks.

Difference in Memory Architecture

ARM microcontrollers often feature a distinct memory architecture compared to desktop systems or even other 8-bit MCUs. These chips usually come with separate regions for code (Flash), data (RAM), and peripherals. Moreover, stack and heap—which are dynamically allocated during runtime—have strict size limitations.

Common Pitfall: Stack Overflow

Unlike PCs, where the operating system provides ample stack and heap, ARM MCUs often supply just a few kilobytes for each. If your blinking-LED project morphs into a complex app with deeply nested function calls or large local arrays, a stack overflow can quickly occur.

Example:

void recursiveFunction(int n) {

char buffer[1024]; // Huge local allocation: DANGER

if (n > 0) recursiveFunction(n-1);

}

Even a few iterations of this function can use up all stack space on an STM32 or LPC chip, blindly causing a hard fault.

Actionable Tip:

- Split large buffers into global or static variables (moved to .data/.bss section).

- Analyze stack usage with your IDE's static analysis or map files.

- Adjust linker script to optimize stack/heap partition.

Alignment Issues

ARM processors commonly require certain data to be aligned on 4-byte boundaries. If C data structures are unaligned, a data access could generate a crash (bus fault) instead of the silent performance penalty seen on x86.

Example:

uint8_t arr[8];

uint32_t val;

memcpy(&val, &arr[1], sizeof(val)); // Potential alignment fault!

Fix: Use memcpy directly to word-aligned addresses or enforce proper alignment using __attribute__((aligned(4))) for GCC or equivalent compiler directives.

Misuse of Pointers and Peripheral Registers

Pervasive pointer usage is one of C's greatest strengths—and sources of subtle bugs. Accessing hardware peripherals means direct C pointer dereferencing to specific MCU memory addresses, but mistakes are treacherous.

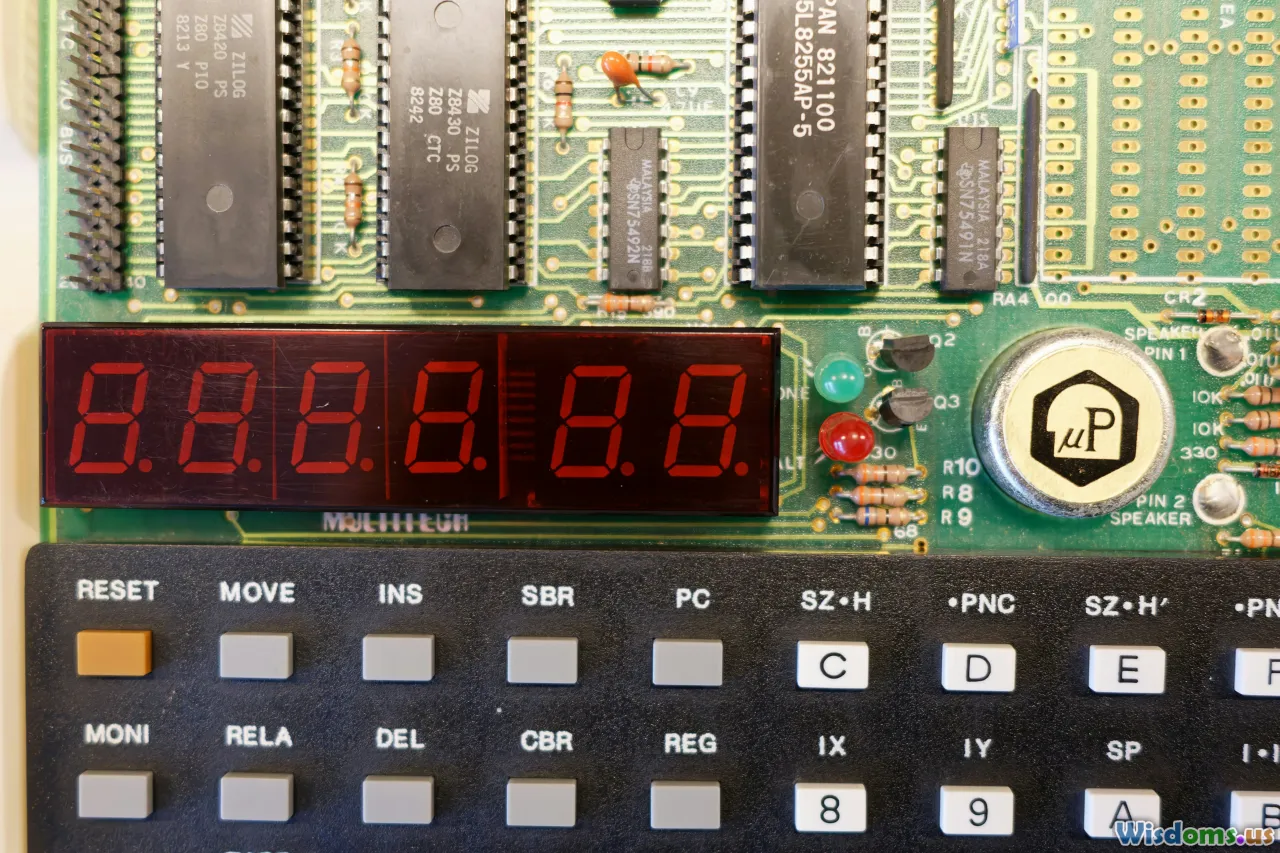

Peripheral Register Map Differences

MCU family changes (STM32F1 to STM32F4, for instance) often mean shifts or additions to the peripheral register memory map. Code that accessed peripheral addresses directly (magic numbers rather than symbolic names) is a recipe for disaster.

Example:

#define REG_GPIO_BASE 0x40010800 // Wrong for all chips!

*(volatile uint32_t *)(REG_GPIO_BASE) = 0xFFFFFFFF; // May crash or overwrite protected memory

Safe Practice:

- Use manufacturer-supplied header files with register definitions (e.g., STM32's

stm32f1xx.h). - Never hardcode peripheral addresses unless absolutely certain through the documentation.

Use NULL and Wild Pointers Carefully

Any attempt to dereference a NULL pointer, uninitialized pointer, or a pointer into unmapped RAM/Flash will generally lead to immediate hard faults on ARM Cortex chips due to the Memory Protection Unit (MPU).

Advice:

- Always init pointers explicitly; memory set to zero does not guarantee valid object assignment.

- Apply static code analysis tools (like

PC-lintorclang-tidy) to catch these code paths.

Interrupt Service Routine (ISR) Hazards

Interrupts are an essential part of embedded systems. Mishandling them, however, is a common cause of microcontroller crashes. If an ISR accesses unprotected shared variables or runs for too long, critical tasks may miss deadlines and cause a watchdog reset or lockup.

Stack Usage within ISRs

Remember, each ISR runs on the main stack, so allocating large local variables inside ISRs is extremely risky.

Example (Don’t do this!):

void USART1_IRQHandler(void) {

char buffer[256]; // Oops! Consumes MCU stack instantly

// ... process

}

Disabling/Enabling Nested Interrupts

Careless enabling or disabling of interrupts can result in accidental re-entry into critical code regions or mask higher-priority interrupts–halting system responsiveness and causing cascading failures.

Best Practices:

- Keep ISRs tiny—process minimal data and delegate work to main code via flags or message queues.

- Never call non-reentrant functions (e.g.,

malloc,printf) from an ISR. - Use volatile keyword for shared variables and consider memory barriers if using multicore ARM MCUs.

Faulty Clock and Power Management Code

The clock tree sets the heartbeat of your microcontroller. If you misconfigure the system clock, ARM MCUs often halt with no obvious explanation until a hardware reset.

Example: Setting a CPU frequency beyond the rated maximum—like cranking STM32’s core over 168 MHz without the right PLL settings—invokes undefined CPU behavior or even device bricking in severe cases.

Issues Include:

- Not waiting for clock sources (like HSE ready flag) before switching

- Failing to update register values for bus prescalers when changing main clock

- Sleep/wakeup bugs: If your software fails to correctly restore registers after returning from STOP or STANDBY mode, peripherals will stall or corrupt data

Safer Coding:

- Carefully track clock configuration APIs provided by vendor libraries

- Use startup code templates and vendor HAL/LL to avoid low-level bugs

- Test all sleep modes and ensure wakeup sources are valid and enabled before deploying

Compiler and Linker Challenges

ARM microcontrollers need a tightly configured toolchain to generate machine code optimized for their instruction set and memory layout. Porting code from desktop C compilers (GCC for x86) to embedded ARM (arm-none-eabi-gcc) reveals numerous issues.

Misconfigured Compiler Flags

If you forget to define MCU-specific flags (like thumb/thumb2 mode or FPU settings), your program might crash as it executes unsupported opcodes or misaligned instruction boundaries.

Example GCC flags for STM32F4xx:

-mcpu=cortex-m4 -mthumb -mfpu=fpv4-sp-d16 -mfloat-abi=hard

Omitting FPU flags while calling floating-point code with hardware floating point can spell disaster.

Linker Scripts: Proper Section Placement

A faulty or default linker script might place initialized variables or the stack in regions that don’t physically exist on the silicon, etc. Many stack overflows are traced to linker malfunctions.

Tip:

- Audit your

*.ldscript—set up precise sections for.text(Flash),.data/.bss(RAM), stack, and heap matching vendor memory map. - Use map files after compilation to verify addresses and sizes of key objects.

- Take advantage of scatter loading and overlays for complex applications that exceed on-chip Flash.

Undefined Behavior Specific to ARM

Certain undefined C behaviors cause manageable bugs on desktop platforms but result in hard faults on ARM MCUs. Some classic blunders include:

Integer Division and Shifts

While most recent ARM Cortex MCUs handle integer division in hardware, mishandling signedness or dividing by zero—something C language does not protect against—results in catastrophic crashes.

Example:

int a = 6, b = 0;

int result = a / b; // On ARM: hard fault

Out-of-Bounds Array Access

Unlike high-level platforms, exceeding array bounds on ARM can cause dereferencing to unmapped memory locations. Safety nets like virtual memory and process isolation do not exist: a single out-of-bounds write might corrupt your interrupt vector table, causing a system-wide cascade of faults.

Strategy:

- Make rigorous use of static and dynamic analysis tools (MISRA, Polyspace, Coverity) to catch boundary errors at compile time.

Misuse of Volatile

ARM's aggressive compiler optimizations magnify issues where the volatile keyword is dismissed. Variables changed by ISRs or DMA must always be declared volatile to ensure correct behavior.

Example:

volatile int adc_complete = 0; // OK for ISR flag

Reference for ARM-specific rationale: ARM Technical Support FAQ

Fault Handling and Debugging Techniques

A crash on ARM is often visible as a hard fault or memory management exception. Unlike computers, there's (usually) no monitor or log file: figuring out why your code failed is a developer’s dark art. Thankfully, ARM Cortex MCUs provide robust mechanisms for root cause analysis.

Using Fault Handlers

Most ARM chips provide exception vectors for faults. Study and customize HardFault_Handler, MemManage_Handler, and BusFault_Handler. The key is to extract and log stack, program counter, and status registers upon fault occurrence.

Advanced debugging snippet:

void HardFault_Handler(void) {

__asm volatile

(

"TST lr, #4 \n"

"ITE EQ \n"

"MRSEQ r0, MSP \n"

"MRSNE r0, PSP \n"

"B hard_fault_handler_c \n"

);

}

Here, you'd pass the context (stack frame pointer) to a hard_fault_handler_c function, log the fault or blink a debug code before system reset.

Breakpoint and Watchpoint Debugging

Modern IDEs (Keil μVision, STM32CubeIDE, IAR) plus JTAG or SWD debuggers allow setting breakpoints, examining memory/registers, and even single-stepping through ISRs or boot code. Hardware watchpoints can halt the system when a target variable is accessed/modified—a powerful tool for tracking stack or heap corruption.

Advice:

- Employ semihosting or ITM (Instrumentation Trace Macrocell) for logging debug output, especially early during the boot sequence.

- Use CMSIS-DAP or similar debuggers for low-level fault tracing, flash breakpoints, and live watch variables.

Vendor HAL Pitfalls and Library Integration

Vendors now supply broad library kits to make peripheral control, middleware integration, and hardware abstraction far easier. Still, misunderstandings when mixing standard C with vendor code can bring the system down.

HAL Initialization Order

Peripheral initialization functions in vendor HAL/LL libraries often have mandatory order of events. For instance, enabling a UART before the system clock or GPIOs are ready triggers erratic failures.

Example Flow for STM32 SPI:

- __HAL_RCC_SPI1_CLK_ENABLE();

- GPIO configuration for SPI pins

- SPI parameter setup

- Enable SPI

Messing up this sequence may not immediately show an error but will produce system halts once operations begin.

IRQ Handler Weak Links

Most vendor libraries provide weak aliases for interrupt handlers. If the naming is incorrect or handler is missing, the default handler loops infinitely, hanging the CPU.

Advice:

- Double-check handler names and signatures in your code—weary copy-paste errors lead to the default panic handler getting invoked.

- Before code changes, track library release notes for any updated or deprecated API.

C and C++ Interoperability Issues

With C++ increasingly popular for embedded work, mishandling C/C++ interoperability—forgetting extern "C" in ISRs or library function prototypes—often causes linkage failure or wrong runtime calls leading to subtle crashes.

Secure Coding Considerations

ARM MCUs are common targets for mission-critical and connected devices—making robust software essential. Basic C coding mistakes lead to exploitable buffer overflows and logic errors, especially where authentication or device reprogramming is involved.

Tips for Safer Embedded C

- Always validate input from external sources—never trust UART/SPI/I2C data

- Limit pointer arithmetic and avoid unchecked buffer copies (

strcpy, usestrncpyinstead) - Enable compiler stack protection flags where available (

-fstack-protector-strongwith GCC/Clang) - Turn on all relevant MISRA-C diagnostic warnings

- Avoid dynamic memory allocation unless absolutely required; if used, tightly limit pool size and usage count

Microcontroller crashes can be mysterious, but every failure mode is rooted in a distinct cause—if you know where to look. As with many other engineering difficulties, forewarned is forearmed. By respecting ARM’s hardware nuances, curating your build process, and learning how to read crash signs, you gain mastery, making your embedded systems both resilient and reliable for the future of connected innovation.

Rate the Post

User Reviews

Popular Posts